WHITEPAPER

# **From Hardware Concept to Zephyr Bring Up—** The Road to Using a Crossover MCU with Zephyr

Eli Hughes, NXP Pro Support Engineer

# Contents

| 1. Synopsis                                               | 3  |

|-----------------------------------------------------------|----|

| 2. "Crossing Over" with i.MX RT685                        | 4  |

| The i.MX RT685 General Purpose CPU Platform               | 4  |

| The PowerQuad Co-Processor                                | 5  |

| CASPER                                                    | 5  |

| Cadence Tensilica® HiFi 4 DSP                             | 6  |

| i.MX RT685 Memory Architecture                            | 6  |

| Inter-processor Communications and Synchronization        | 8  |

| i.MX RT685 Audio Peripherals                              | 8  |

| General Purpose Connectivity and Timers                   | 9  |

| I3C                                                       | 10 |

| 3. The Minimal Configuration i.MX RT685 Hardware Project. |    |

| Codename "Super-Monkey"                                   |    |

| i.MX RT685 PCB Layout Consideration: The VFBGA176 Package | 12 |

| i.MX RT685 Power                                          | 14 |

| Understanding the i.MX RT685 Power Supply Strategy        | 15 |

| +1.8v "Always-On" and Analog Functions                    | 15 |

| User IO                                                   | 15 |

| Power Management Options for the i.MX RT685               | 16 |

| i.MX RT685 Flash Memory Interface                         | 17 |

| FlexSPI Flash Controller                                  | 17 |

| QSPI on FlexSPI Port A Configuration and Boot             | 18 |

| Boot Configuration                                        | 19 |

| Programming and Debug                                     | 19 |

| ISP Serial Boot Support Software                          | 20 |

| i.MX RT685 Debug                                          | 22 |

| Realizing the Super Monkey Hardware                       | 23 |

| SuperMonkey Board Build                                   | 25 |

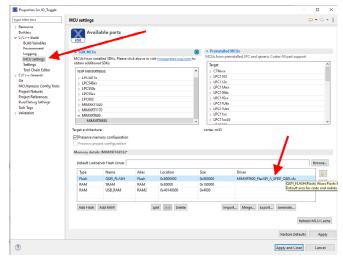

| Bare Metal Bring Up with QSPI Flash                       | 26 |

| The i.MX RT685 Boot Header                                | 27 |

| MCUXpresso IDE + MCU-Link                                 | 29 |

| Programming and Debug with Segger J-Link + Segger Ozone   | 29 |

| 4. Zephyr RTOS Bringup on the i.MX RT685 SuperMonkey      |    |

| A bit about Zephyr boards                                 | 31 |

| Getting Setup for Custom Board Development                | 32 |

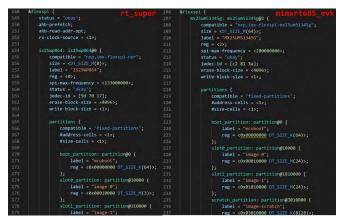

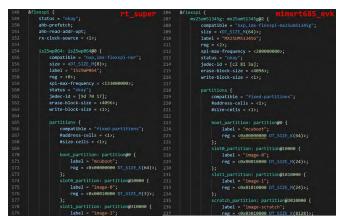

| Seeding your custom board using the RT685 EVK             |    |

| Notable Customizations for the SuperMonkey                |    |

| Board Device Tree Overlay                                 | 35 |

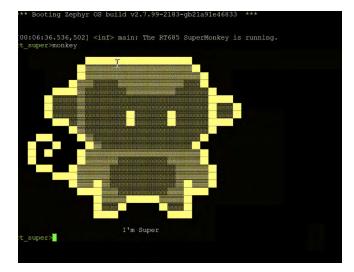

| Final Results                                             |    |

# 1. Synopsis

The intent of this article is to illustrate a hardware design that uses a "crossover" microcontroller (MCU) and the steps needed to bring-up Zephyr RTOS on the custom hardware. I purposely chose a specialized component that represents a slightly more challenging design task. I thought it would be instructive to show a path going from concept to hardware design through booting the RTOS. I do want to point out that this article will dive deep into both hardware and software as a system; when stakeholders have their feet planted on both sides of the hardware/software fence, a team can often do more with less. In all successful projects, understanding the design choices context is key to success.

Over the course of my career, I have had the privilege to observe the complexity of microcontrollers grow orders of magnitude. It certainly has been a wild ride since I was first experimenting with a 6502 as the number of peripherals, memories, and additional co-processing functions now integrated is mindblowing. Managing complexity in a design, both in the hardware and firmware domains, is paramount to "getting things done". Simply coming up with a way to manage your build system and the software components can be a full-time job as you start dealing with more complicated devices. With the introduction of "Crossover MCUs" such as the i.MX RT family from NXP, the demarcation between MCU, Digital Signal Processor (DSP) and application processor is no longer clear, and managing system complexity can be an overwhelming task with the amount of resources in a device.

There are applications where one may desire to directly program specialized hardware elements in an MCU to achieve maximum performance and flexibility. However, having tools for the common/general-purpose functions can really assist with managing the overall system complexity, and will pay dividends. I have always used my hometown street layout as a useful analogy when considering software tools. With a small population of 1000 people, a single stop sign in the center of town can be sufficient for managing traffic flow. However, as population increases by orders of magnitude to 10k or 100k citizens, it would be unwise to not have systems in place to manage the traffic.

Likewise, when engineering any complex microcontroller system, an RTOS can be your "traffic lights" and "highways" to ensure the overall system behaves well as you add complexity. Even if you don't use the RTOS for everything in the system, it can be very helpful with managing general-purpose functions so you can focus on the specialized components. One aspect of the Zephyr RTOS that I find helpful is that you can use as little or as much of the ecosystem as you like. I have found that this aspect gives me a great deal of flexibility when I am actively figuring out how to manage system complexity as I can laser focus on the pieces that are most important.

# 2. "Crossing Over" with i.MX RT685

To set the stage, I want to spend some time examining an interesting device that represents the quintessential blurring of MCU, DSP and applications processor. I will spend some time pointing out some interesting aspects of this device as there are elements that are new in the microcontroller realm. There is quite a bit of detail here, but I want to make a case that this new class of MCUs demand consideration when planning the management of your software system complexity.

It was October of 2017 when the concept of the "Crossover" MCU was first introduced with the NXP i.MX RT1050. For a microcontroller & DSP enthusiast such as myself, the concept of a high clock rate MCU that could tackle problems previously relegated to application processors was very intriguing. I generally approach problems from the perspective of "simplicity". For many real-world processing challenges, microcontrollers can be the simplest solution. There are applications however that demand more real-time processing capability on continuous streams of data. Whether it be high channel count audio, or complicated sensor fusion, there are situations where you need more than what a traditional microcontroller can offer. In some cases, one may choose to go down the path of an applications processor, but this approach is not always optimal when low latency, real-time response is a critical requirement.

The typical method to approach this problem was to use a "Digital Signal Processor" (DSP). DSPs generally have an internal processing pipeline highly tuned to real-time sample by sample data processing. DSPs are great solutions, but you often must give up many of the general-purpose features found in a microcontroller. I encounter this scenario quite often and it is not uncommon to pair a general-purpose microcontroller with a dedicated DSP in an application architecture to get the best of both worlds. My first experience with a DSP architecture was with the Motorola 56K series. It was a powerful tool for crunching numbers, but I found that most of my designs with a DSP also required a general-purpose microcontroller for the traditional IO and connectivity.

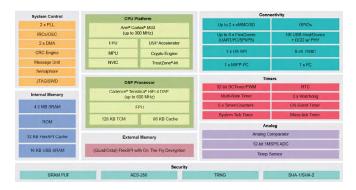

This is where the <u>i.MX RT685</u> steps in. The i.MX RT685 crossover MCU is a newer member of the i.MX crossover family focused on real-time number crunching applications such as audio, sensor fusion and machine learning.

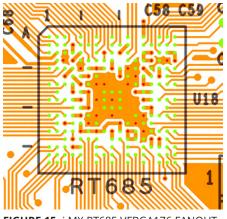

FIGURE 1. THE i.MX RT685.

The i.MX RT685 addresses the audio and sensor fusion challenge by integrating a high-performance 300MHz general purpose microcontroller with a powerful 600MHz DSP processor, a large 4.5MB SRAM bank and a plethora of traditional peripherals & IO.

# The i.MX RT685 General Purpose CPU Platform

The CPU platform in the i.MX RT685 is based upon the Arm® Cortex®-M33 core (CM33). By itself, the CM33 is capable of sophisticated audio applications. The CM33 is built on the Armv8-M architecture which includes **Single Instruction on Multiple**  Data (SIMD) as well as Multiply and Accumulate

(MAC) instructions. There is quite a bit that could be accomplished with CM33 running at 300MHz before even considering the additional DSP core. Last year, I wrote quite a bit about the LPC5500 series MCUs focusing on the LPC55S69 and its ample processing capabilities. The LPC55S69 is also based upon the CM33 core (running at 150MHz vs 300MHz). I think of the i.MX RT685 as a serious upgrade to the LPC55 when you need more of **everything**.

| CPU Pla                            | atform          |

|------------------------------------|-----------------|

| Arm <sup>®</sup> Cort<br>(up to 30 |                 |

| FPU                                | DSP Accelerator |

| MPU                                | Crypto Engine   |

| NVIC                               | TrustZone®-M    |

FIGURE 2. THE i.MX RT685 GENERAL PURPOSE CPU PLATFORM.

One feature of the CM33 is a coprocessor interface which can be <u>accessed with special assembly</u> <u>language instructions.</u> There are two "co-processors" attached to the CM33 in the i.MX RT685: The PowerQuad (labeled as the DSP Accelerator) and the CASPER (labeled as the Crypto Engine).

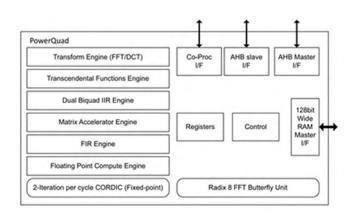

## The PowerQuad Co-Processor

The PowerQuad is a dedicated hardware unit that runs in parallel to the CM33 core inside the i.MX RT685. By using the PowerQuad to work in parallel to the CM33, it is possible to implement sophisticated signal processing algorithms while leaving your general purpose CM33 core available to do other tasks such as communication and IO.

FIGURE 3. THE i.MX RT685 POWERQUAD CO-PROCESSOR.

For the <u>LPC55S69</u> release, I wrote four articles on the PowerQuad and detailed some of its use cases:

- PowerQuad Part 1 Industrial IOT, OFDM. Communications and Smart Metering

- PowerQuad Part 2 Digital IIR Filtering

- PowerQuad Part 3 Fast Fourier Transforms

- PowerQuad Part 4 Matrix and Vector Processing

The key takeaway here is that before we have even considered the additional DSP core, the i.MX RT685 offers a powerful hardware co-processor that can do very useful operations "out of the box". We can be crunching Fast Fourier Transforms (FFTs) at a high rate before even tapping into any of the resources of the DSP or CM33 cores!

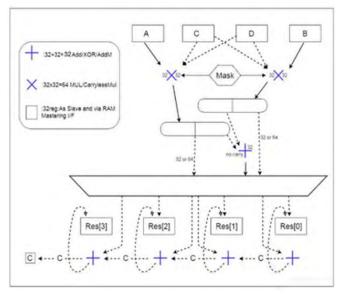

# CASPER

CASPER is an accelerator attached to the CM33 coprocessor interface that is optimized for cryptographic computations. At its core, CASPER is a dual multiply-accumulate-shift engine that can operate on large blocks of data. Applications of CASPER include accelerating cryptographic functions such as public key verification (e.g., TLS/SSL) and computing HMAC signatures. Once again, before we have even considered using the Tensilica© HiFi4 DSP in the i.MX RT685, there is another accelerator in the i.MX RT685 that can offload complicated operations. Many connected products require multiple cryptographic operations and CASPER is a great way of implementing the functions without taxing your other processing pipelines. There are plenty of examples included in the MCUXpresso SDK for utilizing the CASPER accelerator. This feature makes the i.MX RT685 well suited to IOT applications.

**FIGURE 4.** THE i.MX RT685 CASPER CRYPTOGRAPHIC ACCELERATOR.

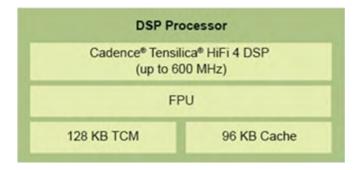

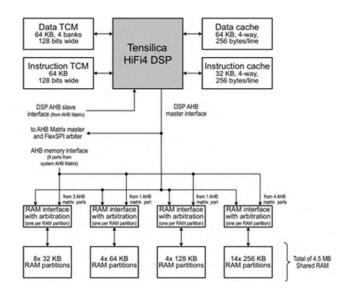

### Cadence Tensilica® HiFi 4 DSP

What makes the i.MX RT685 really interesting is the inclusion of a Cadence Tensilica® HiFi4 DSP core. I previously mentioned that it is certainly possible to implement DSP in the general purpose CM33. There are situations however where a dedicated DSP processing pipeline is needed to achieve a required throughput. One of the limitations of the Cortex<sup>™</sup>-M core is that several cycles can be used just initializing registers before utilizing the SIMD/DSP instructions. In many cases, the SIMD/MAC instructions can execute in a single cycle, but several CPU cycles are required for general purpose registers loaded with input data. Dedicated DSP processors are optimized to allow for continuous processing of single cycle MAC operations

using features such as circular indexed memory modes and zero overhead loops. The HiFi4 DSP supports four 32x32-bit MACs and the ability to issue two 64-bit loads per cycle. There is a vector floating point unit providing up to four single-precision IEEE floating point MACs per cycle. All HiFi4 operations can be used as intrinsics in standard C code.

FIGURE 5. CADENCE TENSILICA® HIFI 4 DSP IN THE i.MX RT685.

The HiFi4 Audio DSP was designed specifically for audio and sensor fusion processing pipelines. It is supported with a large 3rd party ecosystem that covers applications such as sensor fusion, real-time audio, noise reduction, sound enhancement and voice processing. There are more than 300 DSP software packages already ported and optimized for the HiFi4 DSP architecture. This means you can get up and running very quickly, and can easily port your own proprietary software, completely in C, while also maintaining or surpassing the performance of assembly on other DSPs. <u>Cadence even offers an</u> <u>optimized version</u> of <u>TensorFlow Lite</u> to enable machine learning and AI applications at the edge.

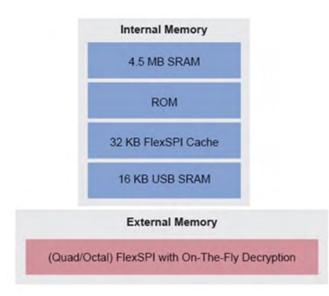

# i.MX RT685 Memory Architecture

Another unique aspect of the i.MX RT685 is its large memory availability and architecture. An important component of an audio processing architecture is the availability of large blocks of memory for time/sample history buffers and fast memories for critical code execution.

FIGURE 6. i.MX RT685 INTERNAL MEMORY.

The availability of 4.5MB of internal SRAM immediately should catch your attention! I tend to think in terms of real-time audio applications for musical performance. 4.5MB of RAM allows for deep buffers to implement delay-based effects including loopers and large time constant reverbs. A 4.5MB pool of fast SRAM removes the need for slower external SDRAM (which is common in many audio DSP architectures). The 4.5MB is shared between the CM33 and the HiFi4 DSP. The memory is sufficiently partitioned to allow for a large amount of flexibility in the processing architecture. There are **30 partitions** across **9 AHB** ports. This means the processing system can be designed to minimize contention between the CPUs and RAM allowing for maximum throughput.

The HiFi4 DSP has dedicated local Tightly Coupled Memories (TCMs) for data and code. Each TCM is 64 KB accessed by a **128-bit port**. The code and data TCMs can be accessed by the Cortex-M33 and by the DMA controllers through a slave port on the AHB matrix. These connections allow the CM33 to bootstrap the HiFi4 with executable code. In addition to the TCMs, there is a dedicated 4-way data cache of 64 KB with 256 bytes per line and a dedicated 4-way instruction cache of 32 KB with 256 bytes per line. The local HiFi4 memory architecture enables the highest level of processing capability as the DSP engine can access code and data with minimal bottle neck.

FIGURE 7. HIFI4 LOCAL MEMORY ARCHITECTURE.

Like many of the other i.MX RT crossover parts, the i.MX RT685 is a flash-less component. This allows the i.MX RT685 to be efficiently built on 28nm FD-SOI semiconductor process technology taking advantage of power consumption savings and clock frequency improvements. Code can be stored in low-cost external Quad/Octo SPI NOR Flash memory. Non-time-critical routines can execute in place from external memory while code requiring better performance can execute from internal SRAM. This approach gives architecture maximum flexibility in balancing cost and performance. It was almost 10 years ago when the NXP LPC4357 was introduced with a QSPI XIP flash interface. The XIP external flash approach has proven to be an effective way to lower the total cost of a solution that can provide large amounts of flash for applications as well as offering flexibility when architecting the MCU solution.

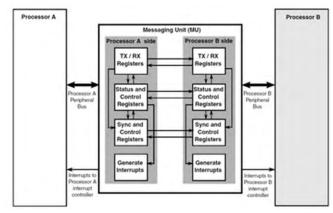

# Inter-processor Communications and Synchronization

Since there are multiple CPU cores in the i.MX RT685, it is important to have hardware support for Inter-Processor Communication (IPC). The i.MX RT685 includes a Messaging Unit (MU) which provides a hardware-based IPC mechanism. While it is possible to set up shared memory between the CM33 and the Hifi4 DSP, the MU offers a way to efficiently send messages/notifications between the processors with interrupt support. The MU is an important component to allow one CPU to wake up another when using power-down modes.

FIGURE 8. THE i.MX RT685 MESSAGING UNIT.

In addition to the MU, the i.MX RT685 includes a hardware enforced semaphore function. Both the CM33 and Hifi4 DSP have access to internal peripherals and memories. It is important to have mechanisms in place to ensure appropriate mutual exclusion. The semaphore unit implements 16 hardware enforced "gates". A processor must write a special sequence to gain access to a hardware gate and to release its lock. The gates are generic in nature and can be used as needed by the software architecture to implement mutual exclusion on both peripherals and memory. Hardware support in the i.MX RT685 for IPC and semaphores make multicore processing simpler to architecture and implement.

# i.MX RT685 Audio Peripherals

Processing audio streams is a key feature of the i.MX RT685. A proper audio "Crossover Processor" would not be complete without hardware peripheral support for common audio IO interfaces. The bread and butter of digital audio is the <u>I2S protocol</u>. I2S is the gateway into a large ecosystem of high-quality external data converters, sample rate converters and audio transmitters (AES3/SPDIF). The i.MX RT685 includes eight multi-function "Flexcomm" serial peripherals. Flexcomm peripheral channels are reconfigurable for all the common serial protocols including USART, SPI, and I2S. Each of the Flexcomm interfaces support four I2S channel pairs for a potential of 32 channel pairs available to the system. All the common digital audio modes are supported in the Flexcomm I2S peripheral including Left justified, Right Justified and TDM (Time Division Multiplexing) modes. The Flexcomm I2S peripheral includes an eight entry FIFO to ensure glitch-less audio streams.

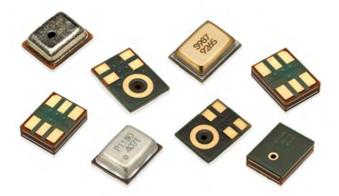

For voice applications, the i.MX RT685 contains a flexible Digital Microphone (DMIC) subsystem. DMICs most commonly use <u>Pulse Density Modulation</u> <u>PDM</u> to encode audio data. A DMIC has no analog output, data is output digitally synchronous to a clock. The clock is supplied by the DMIC subsystem, and its frequency is at a binary multiple (e.g., 64x) of the audio sample rate. DMICs are an extremely popular replacement to older electret microphone technologies as they are small, can be built on a repeatable semiconductor process and have a direct digital interface. As an example, <u>Knowles Acoustics</u> manufactures DMICs for applications including voice and ultrasonic sensing.

FIGURE 9. KNOWLES ACOUSTIC DIGITAL MICROPHONES.

PDM data streams require a digital filter and decimation to recover the audio waveform. The DMIC subsystem in the i.MX RT685 has the necessary hardware to directly connect and decode PDM data streams. Up to eight microphones are supported with flexibility over decimation and sample rate control. Processing an acoustic array of microphones is now much simpler with the i.MX RT685!

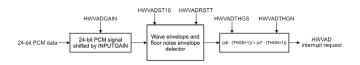

Also included in the DMIC subsystem is a hardware voice activity detector (HWVAD). The HWVAD is a dynamic envelope detector that can be used to trigger /wakeup processing functions when activity is detected in a digital audio stream.

FIGURE 10: i.MX RT685 HARDWARE BASED VOICE ACTIVITY DETECTOR.

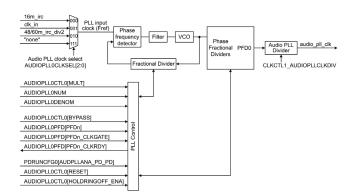

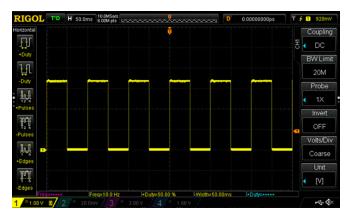

One last important component that I want to mention (that is important to audio applications) is a dedicated Phased Locked Loop (PLL). Audio IO protocols require a dedicated master clock that is at some binary multiple of the target sample rate. When using common audio sample rates such as 44.1KHz or 48KHz, the master clock may not easily be derived from an internal MCU clock source. For example, it is common to observe a 12.288MHz or 24.576MHz master lock when working with 48KHz audio streams. The i.MX RT685 includes a dedicated PLL for audio applications.

FIGURE 11. i.MX RT685 AUDIO PLL.

### General Purpose Connectivity and Timers

With all the dedicated hardware for audio and sensor fusion workloads, there is still a great deal of support in the i.MX RT685 for general purpose connectivity, timing, and analog integration.

| Conn                                                               | ectivity                           |

|--------------------------------------------------------------------|------------------------------------|

| Up to 2 x eMMC/SD                                                  | GPIOs                              |

| Up to 8 x FlexComm<br>(UART/I <sup>2</sup> C/SPI/I <sup>2</sup> S) | HS USB Host/Device<br>+ DCD w/ PHY |

| 1 x HS SPI                                                         | 8-ch. DMIC                         |

| 1 x MIPI®-PC                                                       | 1 x PC                             |

| Tim                                                                | ers                                |

| 32-bit SCTimer/PWM                                                 | RTC                                |

| Multi-Rate Timer                                                   | 2 x Watchdog                       |

| 5 x Timer/Counters                                                 | OS Event Timer                     |

| System Tick Timer                                                  | Micro-tick Timer                   |

| Ana                                                                | log                                |

| Analog Co                                                          | omparator                          |

| 12-bit 1M                                                          | SPS ADC                            |

| Temp 5                                                             | Sensor                             |

**FIGURE 12.** I.MX RT685 CONNECTIVITY, TIMERS AND ANALOG INTEGRATION.

The i.MX RT685 has all the standard connectivity support you would expect including two SD/eMMC interfaces and high-speed USB. One aspect of NXP microcontrollers that I love are the plethora of timers! Two of my favorites being the State Configurable Timer (SCT) and the Multi-Rate Timer (MRT). I have previously written about interesting applications such as <u>ultrasonic pulse pattern generation</u> with the SCT and <u>Modbus communication with an RS485 enabled</u> <u>UART and the MRT</u>. The built-in analog system includes a 1MSPS ADC and analog comparator which can allow the i.MX RT685 to be used into interesting industrial applications that require sensor fusion.

# I3C

One last unique feature that I want to point out in the i.MX RT685 is the addition of a MIPI® I3C interface. I3C is a super set of the classic I2C bus. I3C was developed by the MIPI alliance to provide an upgrade to the I2C for mid-speed applications. It is positioned as an alternative to SPI while keeping a simple two wire interface between devices on a PCB. It is widely expected that I3C will be a standard interface on many new sensors and peripheral components. Some notable features:

- ► Up to 12MHz clock rate. SDA and SCL lines use both open-drain and push-pull modes to increase data rate and allow bi-directional communications

- "In Band Interrupts". A peripheral can interrupt a controller over the bus without extra pins.

- Multi-Controller/Multi-Drop

- Double data rate modes that offer transfer speed on parity with classic SPI

- Hot Joins. Nodes can join the bus at any time.

Nodes get notifications when a new device joins the bus.

- ► Backwards compatibility with I2C.

- Dynamic Addressing

- ► In-Band Common Command Codes to standardize behaviors.

I3C is looking very cool and offers a unique blend of I2C and SPI capabilities. Be sure to get informed on I3C as you will see a lot more of it in years to come.

I hope this overview of the i.MX RT685 was able to get you interested in the crossover processor concept and its unique capabilities. My background in acoustics, audio and sensor fusion always steer my interests to parts with a diverse mix of capabilities. From my perspective, it is one of the most interesting MCU platforms currently available. I was only able to hit on the highlights and I hope you can find you way to the <u>i.MX RT685 website to learn more.</u>

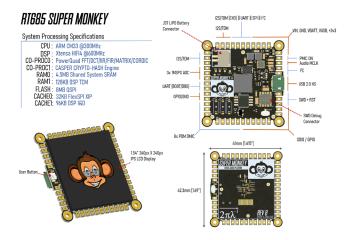

# 3. The Minimal Configuration i.MX RT685 Hardware Project. Codename "Super-Monkey"

When starting a new design, the most prudent path is to purchase an EVK for a new MCU. Zephyr has support for the i.MX RT685 EVK in the mainline repository. Since the i.MX RT685 is more complicated than most microcontrollers, I did want to show a custom design that deviated from the EVK. This design serves as an example of the steps needed to get Zephyr running on a custom board. The i.MX RT685 requires a bit more care and feeding to get a project up and running and I thought it would be good to have an example available for others to use. The part is offered in a 0.5mm pitch VFBGA176 so I also thought it would be good to show a minimal configuration example that can be built with low-cost PCB technologies.

I find this step to be a very useful exercise as highend MCU's can be overwhelming, especially to those coming from a traditional MCU background. The goal here is to develop a simple "minimal configuration" example and build it for a demonstration. There are resources available to helping you design with the i.MX RT685 such as the "Hardware Development Guide for the RT685 Processor" (RT685HDUG) and the <u>MIMXRT685-EVK</u>. These resources can help bootstrap your next design. My personal view is that having several different design perspectives is always beneficial. Between the existing reference material and this article there should be enough information to start your next i.MX RT685 design with confidence.

In 2020, I did similar project codenamed <u>"Mini-</u> <u>Monkey" using the LPC55S69 in its VFBGA98 package.</u> It was an exercise to illustrate a simple project using the 0.5mm VFBGA98 package on a low cost 2-layer PCB process. That hardware project demonstrated the LPC55S69 being able to do things like <u>microphone</u> <u>capture</u>, <u>visualization</u> and <u>animated GIF decoding</u>. The i.MX RT685 is definitely a <u>"step up</u>" from the LPC55S69 and is well suited to high end audio applications. Between the 300MHz CM33, the PowerQuad coprocessor and the 600MHz tensilica HIFI4 DSP, there is quite a bit of horsepower for your application! It was obvious to me that the i.MX RT685 could be a great fit for all my future real-time DSP audio processing projects. In 2011, I built the <u>"Active Pickguard"</u> demonstrating what could be accomplished with the Kinetis K20 (Cortex-M4) device.

10 years later there have been some serious advances in embedded technologies. Rev 2 of the Active pickguard has been in the back of my mind for a while now and the i.MX RT685 is a potential great fit!

To run some experiments with the i.MX RT685 in-situ, I want to design a small module that bootstraps the i.MX RT685 with everything I need for my high-end audio applications. Since I may go through several iterations, I thought a simple module (like the <u>Mini-</u> <u>Monkey</u>) would be a good start point. To get the project "out the door", it is important to set clear boundaries at the outset. I do not need the module to bring out all the features of the i.MX RT685. The initial goal is to get the most critical IO to get my audio projects moving. Iteration is very important in the engineering process so I thought I would keep it simple to keep momentum going. Since the .MX RT685 is a significant step up in performance from the LPC55S69 base Mini-Monkey, I thought the codename "Super-Monkey" would be a good fit. It leaves me with options for future projects (hint hint!). Ultra-Monkey, Mega-Monkey, Nano-Monkey....

My Initial Specs for the i.MX RT685 Super-Monkey Module:

- ► IO breakout for 8 digital microphones (DMICs)

- One TDM input for up to 8-channel audio in (one flexcomm channel)

- Two separate I2S audio output channels. One will be for outputting audio and the other will be a special monitor (two flexcomm channels)

- I3C Access. This is a new feature I have been wanting to experiment with

- ► Solder pads to add an <u>optional TFT display</u>.

- ▶ SWD debug access

- ▶ USB connector for ISP boot and power

- ► A debug UART

- ► A handful of GPIO

- ► +5v power via USB or IO pins

- On board Flash (the i.MX RT685 is a flash-less part)

- Crystal/clock management

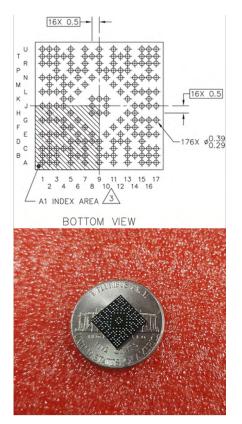

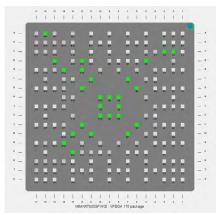

# i.MX RT685 PCB Layout Consideration: The VFBGA176 Package

The first order of business when I approach a new hardware design is to understand the device package and any implications of the pin geometries. For the Super-Monkey project, I will be designing with the MIMXRT685SFVKB which uses the VFBGA176 package. The VFBGA176 is a 9mm x 9mm ball grid array (BGA) with 0.5mm pitch. A fine pitch BGA package can be intimidating, especially for those who may only have experience with microcontrollers in QFP packages. One of the reasons I built the <u>"Mini-Monkey"</u> was to demonstrate that the LPC55S69 VFBGA98 package option was doable with a 2-Layer process and low-cost design rules. The VFBGA176 was designed to be easy to fanout and is routable with a practical 4-layer process.

FIGURE 13. THE VFBGA176 PACKAGE.

I enjoy studying unique BGA ball arrangements. This package is a work of art. Notice that there are several regions left unpopulated making it simpler to fan out. In many cases, a 0.5mm BGA requires a filled micro via-in-pad to fanout the IO. There was quite a bit of thought put into the pinout of the i.MX RT685 and it is possible to fan this device out without via-inpad technology. Many of the balls on the interior are VSS connections. Using the <u>MCUXpresso IDE</u> pin tool, one can highlight pins and get a rough sense of the layout strategy.

FIGURE 14. SIGNAL HIGHLIGHTING WITH THE MCUXPRESSO IDE PIN TOOL

I spent some time analyzing the Gerber files from <u>i.MX RT685EVK</u> to get a feel for the layout. The fanout of this package is very practical.

FIGURE 15. i.MX RT685 VFBGA176 FANOUT

Notice that all the signal pads can be fanned out on the top layer. The via connections (red dots) are to connect to the power & return planes on inner layers. The vias are placed in the depopulated ball regions. The IO fanout on the RT685EVK uses 3mil width/ 3mil space geometry. The vias under the device package use 6mil drills. These geometries are a bit tighter than what is typically required by traditional microcontrollers, but it is well within the capabilities of many PCB fab houses.

Since the only vias used in the fanout are for power and returns, there is plenty of space to place decoupling capacitors on the opposite side of the PCB. Figure 16 illustrates the placement of the decoupling caps on the RT685EVK. They are nearby existing vias to direct feed the power planes.

FIGURE 16. RT686 VFBGA176 DECOUPLING CAPACITOR STRATEGY

Many 0.5mm pitch BGAs require via-in-pad technology along with blind/buried stack-ups so the fanout vias do not interfere with the decoupling capacitors on the opposite side of the PCB. In the case of the VFBGA176, we can use lower cost processes as we do not need via-in-pad technology or a blind/buried stackup. Fanout and decoupling capacitor placement is straightforward for the i.MX RT685 VFBGA176 package. I really like to understand package geometry before I start a design as it can directly influence other decisions down the pipeline. The time spent analyzing the Gerbers on the RT685EVK was well spent as I now have confidence the fanout of the part will not require any exotic PCB process technology.

### i.MX RT685 Power

Once I study the packaging for a new MCU, the next order of business is to understand the power supply architecture. MCU power supply design is intertwined with PCB layout strategy, so it is a good idea to understand both early in the design process.

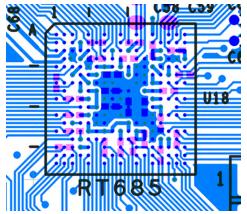

The i.MX RT685 crossover MCU power/performance ratio sits at an intersection of traditional MCUs, dedicated DSPs and application processors. To get significant clock rate improvements over traditional MCUs, the i.MX RT685 was built on <u>28nm FD-SOI process</u> <u>technology</u>. Using 28nm process technology for an MCU is a new concept that NXP has helped pioneer.

FIGURE 17. 28NM FD-SOI PROCESS TECHNOLOGY.

If you remember your electrical engineering coursework, all the major characteristics of a MOSFET are controlled by geometry. FD-SOI process technology has many advantages, one being that we can bias the body of the MOSFETs dynamically. Body biasing gives us real-time programmatic control over the MOSFET threshold voltage VTH. For MCU applications, we can move VTH up or down allowing one to increase clock frequency/performance or reduce dynamic power consumption.

From the perspective of production yield and a desire for increased CPU clock rates, the geometries of the transistors need to be pushed to their design rule minimums. A byproduct of small transistor geometries is a numerically small value for MOSFET VDS. For 28nm FD-SOI process technology, the nominal MOSFET VDS has been characterized to 1.0v nominal. This means the "core" logic power must be derived from a 1.0v supply.

#### Why are many MCUs powered at +3.3v?

Even though 28nm FD-SOI is 1.0v nominal, one can imagine the maximum allowed VDS to also scale up with geometry. You might not be aware, but many +3.3v MCUs might still have cores that need +1.2v, 1.8v or 2.5v core power because of the underlying process technology. The MCU will usually incorporate an LDO that the end user may not be aware of. Sometimes this internal LDO is documented in the device datasheet, but it might not always be the case.

As the core voltage requirements are pushed lower, the internal LDO approach can get more inefficient resulting in additional power dissipation in the IC package. The core logic is one of the largest consumers of dynamic power resulting from all the MOSFETS switching at a high clock frequency. As the core logic voltage requirement drops, it is important to have direct access to the core power domain to directly supply power from a switching DC-DC converter. As an example, the NXP LPC55S69 is built on 40nm process technology and uses a 1.2v core. It integrates its own switching DC-DC converter to minimize active power dissipation.

# Understanding the i.MX RT685 Power Supply Strategy

The i.MX RT685 has three general power domains:

► +1.0v Core

VDDCORE

- ▶ +1.8V for "Always-On" and Analog Functions

- ► +1.71 to +3.6v capable IO (which can be further divided into 3 distinct groups)

#### i.MX RT685 Core Power

VDDCORE is used to power the internal CPU(s) and core logic. To maximize clock rate, the CPUs and core logic are constructed from the smallest transistors allowed by the process technology design rules. In the case of the i.MX RT685 and 28nm FD-SOI, the core voltage is nominally 1.0v. Looking at the i.MX RT685 datasheet, the maximum allowed value does not give one much room for error in your power supply!

It is possible to operate the core power at values lower than 1.0v as to save power when using lower clock frequencies. NXP provides a power library which can tune the body bias to achieve low power consumption figures at lower clock rates.

Power supply for core logic

The take-away here is that by providing a separate core power supply access, the designer has flexibility in how to optimize for a particular use case. It is important to note that the i.MX RT685 includes an LDO that can be powered from a +1.8v rail. Use of the LDO is not required but is available if the efficiency of a switching power supply is not required.

# +1.8v "Always-On" and Analog Functions

There are several 1.8V rails in the i.MX RT685 that may be combined if needed. One of these 1.8v rails is the "always-on" power domain. This domain is used for features that must be active in power down states such as the RTC, reset, optional LDO and PMIC control. In addition to the +1.8v "always-on" domain, there are +1.8v rails for other analog functions such as the ADC and comparator. +1.8v power is required for the i.MX RT685 in a minimal configuration scenario.

### User IO

1.155

Lastly, the IO pins can be powered separately from the +1.8v functions and the core. The IO supply range

is +1.71 to +3.6v with +3.3v being the most common. There are other circumstances however when you may want certain IO pins to use +1.8v. For example, many high-speed double data rate quad/octo NOR flash devices operate with a +1.8v power supply. The i.MX RT685 has 3 separate IO banks so you can have a mix of IO voltages. In a minimal configuration scenario, it would be possible to power all the IO from +1.8v reducing the number of DC-DC converters needed in a system. However, it is most likely one will require some IO at +3.3v.

|            | Tamb = 0 °C to +       | eral operating conditionscontinued<br>85 °C, unless otherwise specified.                                                    |                                               |      |        |       |      |  |

|------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|--------|-------|------|--|

|            | Symbol                 | Parameter                                                                                                                   | Conditions                                    | Min  | Typ[1] |       | Unit |  |

|            | VDDCORE 2              | Low voltage operating range.<br>SDK Power Library version = 0x020300,                                                       | Active Mode<br>(DSP Max Freq = 115 MHz, FBB). | 0.7  | •      | 1.155 | v    |  |

|            |                        | SDK version 2.8.3 and later. 85                                                                                             | Active Mode<br>(DSP Max Freq = 260 MHz, FBB). | 8.0  |        | 1.155 | v    |  |

|            |                        |                                                                                                                             | Active Mode<br>(DSP Max Freq = 375 MHz, FBB). | 0.9  | •      | 1.155 | V_   |  |

| FIGURE 18. |                        | Full voltage operating range.<br>SDK Power Library version = 0x020300,                                                      | Active Mode<br>(DSP Max Freq = 70 MHz, FB8).  | 0.7  |        | 1.155 | v    |  |

| i.MX RT685 |                        | SDK version 2.8.3 and later. 25                                                                                             | Active Mode<br>(DSP Max Freq = 195 MHz, FBB). | 8.0  | •      | 1.155 | v    |  |

| VDD CORE   |                        |                                                                                                                             | Active Mode<br>(DSP Max Freq = 300 MHz, FBB). | 0.9  | •      | 1.155 | v    |  |

|            |                        |                                                                                                                             | Active Mode<br>(DSP Max Freg = 480 MHz, FB8). | 1.0  | •      | 1.155 | v    |  |

|            |                        |                                                                                                                             | Active Mode<br>(DSP Max Freq = 600 MHz, FBB). | 1.13 | •      | 1.155 | v    |  |

|            | VDDCORE<br>(2151/91/7) | Power supply for core logic. On-chip<br>regulator not used. Power supplied by<br>an off-chip power management IC<br>(PMIC). | Retention Mode                                | 0.7  |        | 1.155 | V    |  |

|            |                        | Low voltage operating range.                                                                                                | Active Mode                                   | 0.7  |        | 1.155 | V    |  |

|            |                        | SDK Power Library version = 0x020300,                                                                                       | (M33 Max Freg = 70 MHz, FBB).                 |      |        |       |      |  |

|            |                        | SDK version 2.8.3 and later.                                                                                                | Active Mode                                   | 0.8  |        | 1.155 | V    |  |

|            |                        |                                                                                                                             | (M33 Max Freq = 150 MHz, FBB).                |      |        |       |      |  |

|            |                        |                                                                                                                             | Active Mode<br>(M33 Max Freq = 220 MHz, FBB). | 0.9  |        | 1.155 | v    |  |

|            |                        | Full voltage operating range.<br>SDK Power Library version = 0x020300,<br>SDK version 2.8.3 and later.                      | Active Mode<br>(M33 Max Freq = 65 MHz, FBB).  | 0.7  |        | 1.155 | v    |  |

|            |                        |                                                                                                                             | Active Mode<br>(M33 Max Freq = 140 MHz, FBB). | 0.8  |        | 1.155 | v    |  |

|            |                        |                                                                                                                             | Active Mode<br>(M33 Max Freq = 210 MHz, FBB). | 0.9  | -      | 1.155 | v    |  |

|            |                        |                                                                                                                             | Active Mode<br>(M33 Max Freq = 275 MHz, FBB). | 1.0  | -      | 1.155 | v    |  |

|            |                        |                                                                                                                             | Active Mode                                   | 1.13 | -      | 1.155 | V    |  |

On-chip regulator not used.

Power supplied by an off-chip

E -0.3

| Power   | r Supply for pins                                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------|

| Pin     | GPIO pins                                                                                                          |

| VDDIO_0 | PIO0_0 to PIO0_13                                                                                                  |

|         | PIO1_11 to PIO1_29                                                                                                 |

|         | PIO2_12 to PIO2_23<br>PIO3_25 to PIO3_31<br>PIO4_0 to PIO4_10<br>PIO7_24 to PIO7_31                                |

| VDDIO_1 | PIO0_14 to PIO0_31<br>PIO1_0 to PIO1_10<br>PIO2_24 to PIO2_31<br>PIO3_0 to PIO3_24<br>PMIC_I2C_SCL<br>PMIC_I2C_SDA |

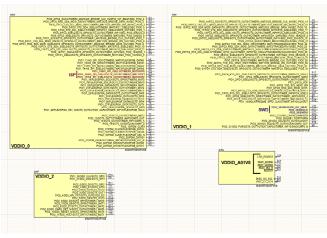

FIGURE 19. i.MX RT685 POWER DOMAIN PIN ASSIGNMENTS

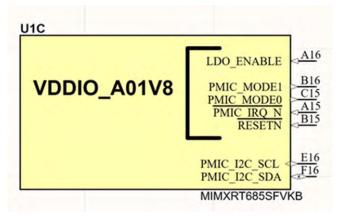

It is important to understand all the IO power options at the outset of a design. It is easy to make a mistake and end up with a non-functional part design. For my own designs, I take extra steps in the schematic entry stage to ensure success. I like to break up the schematic symbol for a part based upon a particular voltage domain. This makes design reviews much simpler as it is easier to spot a mistake. For example, reset in the i.MX RT685 is in the +1.8v "always-on" domain. Make sure it is clearly marked so you do not pull it to +3.3v!

FIGURE 20. i.MX RT685 IO SCHEMATIC BLOCKS

# Power Management Options for the i.MX RT685

The power architecture for the i.MX RT685 is more complicated than a traditional single voltage rail MCU because of its flexibility. However, once you understand the architecture, the application design is straightforward. For example, in a minimal configuration that requires +3.3v IO, one could power the i.MX RT685 with +3.3v and +1.8v using the internal LDO for the core.

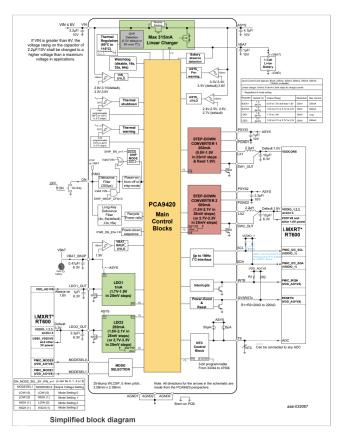

NXP offers an integrated solution that makes powering the i.MX RT685 much simpler: the PC4390 Power Management Integrated Circuit (PMIC). A PMIC is essentially a handful of DC-DC converters, LDOs and control circuitry integrated into a single package.

FIGURE 21. THE PCA9420 PMIC

In the case of the <u>PCA9420</u>, it has been specifically designed to power the i.MX RT685. The out of the box configuration will perform all the necessary sequencing to bring up the device correctly. It is packaged in a 24-pin QFN package which is extremely compact given the number of functions it is providing. The PCA9420 also provides reset control and has an I2C interface that allows the supplies to be tuned for the different clocking configurations.

FIGURE 22: i.MX RT685 DEDICATED PMIC INTERFACE

I highly recommend using the PCA9420, especially if this is the first design iteration using the i.MX RT685. A designer is certainly free to use other power management solutions but the PCA9420 is a path to ensure success. If your application requires any power management and sleep functions, then the PCA9420 is an optimum choice. The Super-Monkey design will be using the PCA9420 to simplify the power supply. I plan on using the PCA9420 on the Super-Monkey as the module will be powered with a single +5v rail.

## i.MX RT685 Flash Memory Interface

When starting with a new MCU, I almost always examine power architecture and device packaging as the topics are often interwoven. Once I have a good idea of how to properly power a part and understand what the PCB layout will look like, the next order of business is understanding boot-up and debugging. Like power & package, boot & debug are also often interconnected. It is important to consider both topics simultaneously. The i.MX RT685 series have additional design considerations as they are flash-less MCUs as the designer must add a flash memory external to the part. The flash-less MCU paradigm allows for flexibility in your design but can be challenging if it is your first experience with a flash-less MCU.

For the Super-Monkey project, I am electing to use a simple external memory configuration with common QSPI NOR flash. In my use case, time-critical DSP algorithms will execute from fast internal RAM. Boot functions and non-critical code can live in the external QSPI flash. I feel this is a good tradeoff for cost, storage capacity and performance. QSPI is now well established in the marketplace and NXP was the 1st to offer execute in place (XIP) technology over a quad SPI bus (QSPI or SPIFI). This technology was introduced over 10 years ago with the LPC18xx and LPC43xx microcontrollers. Since then, QSPI XIP has proven to be a very good choice for many applications. It is very common for real-time audio/DSP code to have a reasonably small footprint and it can execute from the fastest internal/tightly coupled memories. Most other system code requirements are well served by XIP from external QSPI (serial communications, USB, system tasks, etc.). It is important to note that the memory controller in the i.MX RT685 has 32KB of cache. A little bit of cache on XIP QSPI memory can go a long way to improve performance.

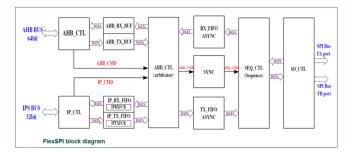

# FlexSPI Flash Controller

Built into the i.MX RT685 is a special flash interface controller called "FlexSPI". FlexSPI supports access to Single/Dual/Quad/Octal flash interfaces through the internal AHB bus. This means the CPU can access SPI memory as if it were a normal memory mapped flash device. The details of the SPI transactions are handled by the FlexSPI controller. FlexSPI enables a wide array of memories to be connected to the MCU. With FlexSPI, designers have access to extremely dense flash memories and can use new flash devices as they become available. Designs can be easily scaled to storage requirements as needed. SPI memories are also easy to route on a PCB as there are fewer connections. Chapter 33 of UM11147 details the FlexSPI controller and possible use cases.

FIGURE 23. NXP FLEXSPI MEMORY CONTROLLER.

The FlexSPI controller has two ports which can be further subdivided into two separate interfaces allowing a maximum of 4 QSPI devices if needed. To support future designs, the controller implements a look up table (LUT) that allows command sequences to be altered. It is also important to note that in addition to flash, there are now SPI based (p)SRAM devices in the marketplace allowing for volatile memory to be added as well.

# QSPI on FlexSPI Port A Configuration and Boot

The MIMXRT685-EVK demonstrates use of the FlexSPI peripheral with two devices attached. One being a high-speed octal pSRAM connected to port A and an octal flash connected to port B. Note the "octal" interface. FlexSPI supports up to 8-bit transactions on a Double Data Rate (DDR) interface. Octal devices are still quite new as compared to quad devices but offer a significant performance increase (4x between the increased data path and DDR interface). I also want to note something important about the FlexSPI on the i.MX RT685. There are two ports, but Port A can

support higher speed transfer through the use of an additional DQS pin. In the case of the RT685EVK, the pSRAM is wired to the higher speed port. I do have to chuckle a bit when the terms "SPI" and "Octal" are combined. These memory interfaces are now synchronously clocked parallel buses. QSPI was a simple extension to traditional 1 bit SPI but has now grown from the simple "serial" use case. For the Super-Monkey, I want to demonstrate a simplified scenario.

There is one other detail important to the i.MX RT685 with regards to the FlexSPI connections:

# *If you want to use all 8 channels of the DMIC interface, FlexSPI B will not be available. You must connect to FlexSPI A.*

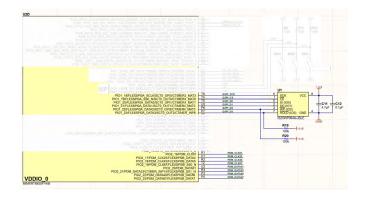

Figure 23 shows how to connect a QSPI flash to the i.MX RT685.

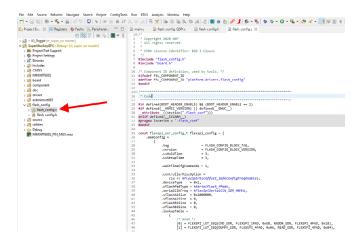

FIGURE 24. QSPI FLASH CONNECTION ON THE i.MX RT685.

As you can see, QSPI memory is simple to connect. I am using a +1.8v flash device. Typically, I arrange my schematic symbols to be group functions by power domain to reduce the chance of error. In this case, VDDIO\_0 will be powered by +1.8v from the PMIC. I left the connections to DMICs highlighted so you can see the intersection with FlexSPI B. MCUXpresso IDE includes a pin tool that allows you to plan the device muxing/pinout to reveal any potential conflicts. With every new hardware design, I create a skeleton <u>MCUXpresso SDK</u> software project that gets included in my hardware design git repository. The skeleton project's sole purpose is to define all of my IO as I am working through the hardware design.

# **Boot Configuration**

Once the flash memory is connected, there are two questions I always ask. How does the CPU know to boot from this external flash and how do I program the flash? The i.MX RT685 series shares a legacy with the LPC family of microcontrollers in that there are a few "ISP" pins which control the boot process. These pins are sampled at power up by routines located in ROM. One of the features in the LPC family of microcontrollers are ROM boot functions/utilities that enable programming over a few different serial interfaces. The i.MX RT685 continues this tradition. Like its LPC predecessors, boot configuration is simple to set up.

| Boot mode                               |      | ISP1 pin<br>PIO1_16 |      | Description                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------|------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | low  | low                 | low  | Reserved                                                                                                                                                                                                                                                                                                              |

| SDIO0 (SD Card)                         | low  | low                 | high | Boot from an SD card device connected to SDIO 1 Interface. The<br>RT6xx will look for a valid image in the SD card device. If there is no<br>valid image found, the RT6xx will enter the ISP boot mode based on<br>OTP DEFAULT_ISP_MODE bits (64, BOOT_CFG [0]) defined in<br>Table 1110 '800T_CFG(0] bit fields".    |

| FlexSPI Boot from<br>Port B             | low  | high                | low  | Boot from Quad or Octal SPI Flash devices connected to the FlexSPI<br>interface 0 Port B. Ter Toxx will look for a valid image in external<br>Quad/Octal SPI Flash device.<br>If there is no valid image found, the RT6xx will enter recovery boot or<br>ISP boot mode.                                               |

| FlexSPI Boot from<br>Port A             | low  | high                | high | Boot from Quad/Octal SPI Flash devices connected to the FlexSPI<br>interface 0 Port A. The RT6xx will look for a valid image in external<br>Quad/Octal SPI Flash device.                                                                                                                                              |

|                                         |      |                     |      | If there is no valid image found, the RT6xx will enter recovery boot or<br>ISP boot mode.                                                                                                                                                                                                                             |

| SDIO 0 (eMMC)                           | high | low                 | low  | Boot from an eMAC device connected to SDIO 0 interface, The RTG/<br>Will look for a valid image in the eMAC device, if there is no valid<br>image found, the RTG/x will enter the ISP boot mode based on the<br>value of OTP DEFAULT_ISP_MODE that (6.4, BOOT_CFG(0))<br>ednhed in Table 110: SDOT_CFG(0) bit hields. |

|                                         | high | law                 | high | Reserved                                                                                                                                                                                                                                                                                                              |

| Serial ISP (UART,<br>SPI, I2C, USB-HID) | high |                     | low  | The Serial Interface (UART, SPI, and I2C,USB-HID) is used to<br>program OTP, external Flash, SD or eMMC device.                                                                                                                                                                                                       |

| 111                                     | high | high                | high | Serial Master boot (SPI Slave, I2C Slave, or UART, USB-HID) is used<br>to download a boot image over the serial interface (SPI Slave, I2C<br>slave or UART, USB-HID).                                                                                                                                                 |

ROM code that cannot be changed.

FIGURE 25. SELECTING FLEXSPI PORT A ON THE ISP BOOT PINS.

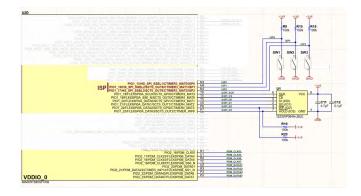

For the Super-Monkey module, I elected to use three switches to control the boot pins. Note that the ISP lines are in the +1.8v power domain. Setting the switches appropriately will allow FlexSPI port A to be used by the boot ROM.

FIGURE 26. i.MX RT685 ISP PIN CONNECTIONS

The i.MX RT685 user manual (Chapter 41) documents how the boot process functions in detail.

# Programming and Debug

An important mode of the ROM bootloader in the i.MX RT685 is called "Serial ISP" which enables a PC/host to perform flash operations (and program OTP fuses) via interfaces such as UART or USB. It is important to \*always\* allow this mode to be available in your designs. It will save a great deal of time and headache down the road.

| Boot mode                               | ISP2 pin | ISP1 pin | ISP0 pin | Description                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------|----------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | PI01_17  | PIO1_16  | PIO1_15  |                                                                                                                                                                                                                                                                                                                          |

|                                         | low      | low      | low      | Reserved                                                                                                                                                                                                                                                                                                                 |

| SDIO0 (SD Card)                         | low      | low      | high     | Boot from an SD card device connected to SDIO 1 interface. The<br>RT6xx will look for a valid image in the SD card device. If there is no<br>valid image found, the RT6xx will entire the ISP boot mode based on<br>OTP DEFAULT_ISP_MODE bits (64, BOOT_CFG (0)) defined in<br>Table 1110 "BOOT_CFG(0) bit fields".      |

| FlexSPI Boot from<br>Port B             | low      | high     | low      | Boot from Quad or Octal SPI Flash devices connected to the FlexSPI<br>interface 0 Port 8. The RT6xx will look for a valid image in external<br>Quad/Octal SPI Flash device.<br>If there is no valid image found, the RT6xx will enter recovery boot or<br>ISP boot mode.                                                 |

| FlexSPI Boot from<br>Port A             | low      | high     | high     | Boot from Quad/Octal SPI Flash devices connected to the FlexSPI<br>interface 0 Port A. The RT6xx will look for a valid image in external<br>Quad/Octal SPI Flash device.                                                                                                                                                 |

|                                         |          |          |          | If there is no valid image found, the RT6xx will enter recovery boot or<br>ISP boot mode.                                                                                                                                                                                                                                |

| SDIO 0 (eMMC)                           | high     | low      | low      | Boot from an eMMC device connected to SDIO D Interface. The RT6xx<br>will look for a valid image in the eMMC device. If there is no valid<br>image found, the RT6xx will entre the ISP boot mode based on the<br>value of OTP DEFAULT_ISP_MODE bits (64, BOOT_CFG (0))<br>defined in Table 110 "BOOT_CFG(0) bit fields". |

|                                         | high     | low      | high     | Reserved                                                                                                                                                                                                                                                                                                                 |

| Serial ISP (UART,<br>SPI, I2C, USB-HID) | high     | high     | low      | The Serial Interface (UART, SPI, and I2C,USB-HID) is used to<br>program OTP, external Flash, SD or eMMC device.                                                                                                                                                                                                          |

| tft                                     | high     | hìgh     | high     | Senal Master boot (SPI Slave, I2C Slave, or UART, USB-HID) is used<br>to download a boot image over the serial interface (SPI Slave, I2C<br>slave or UART, USB-HID).                                                                                                                                                     |

Table 992 shows the ISP pin assignments and is the default pin assignment used by the ROM code that cannot be changed.

Serial ISP can be your "escape hatch" when you are having issues or need a production programming/ configuration interface. At minimum, you should always provide access to the UART lines on Flexcomm 0 (PIO0\_1 / PIO0\_2).

FIGURE 28. SERIAL ISP UART PINS

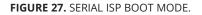

I cannot stress how important it is to have access to these pins! In addition to the UART, I would also recommend having USB access as well. The ROM bootloader enumerates a USB-HID device for access to the programming/test functions. There are minimal parts required to enable the USB interface. I always add some EMI filtering to the +5v VBUS line as well as some ESD protection to the D+/D- lines.

FIGURE 29. i.MX RT685 MINIMAL USB CONNECTIONS.

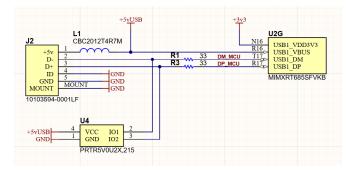

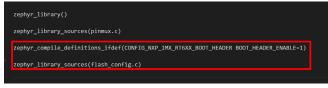

I do want to point out the minimal clocking configuration required by the ROM bootloader. A 24MHz crystal is required for correct USB operation.

FIGURE 30. i.MX RT685 MINIMAL CRYSTAL/CLOCK CONFIGURATION.

I am not using the RTC and elected to not connect a 32KHz crystal. For the minimal configuration scenario, a 24MHz crystal is the path to quick success.

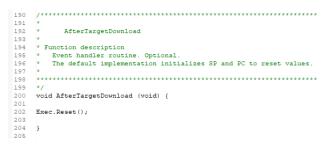

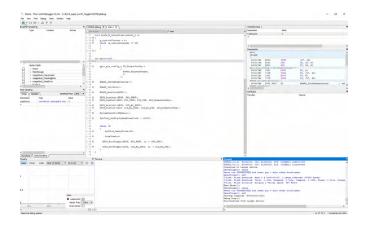

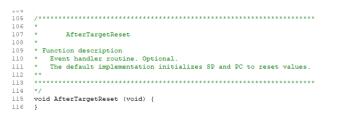

## ISP Serial Boot Support Software

There are a couple of useful software tools to drive the serial ISP boot functions. The first is a command line application "blhost". The i.MX RT685 reference manual has some examples of the different uses of blhost (see chapter 41). blhost can program externally connected flash, discover timing parameters, and program internal OTP fuses. It is a Swiss Army Knife that is very useful for testing, debugging and deploying your design.

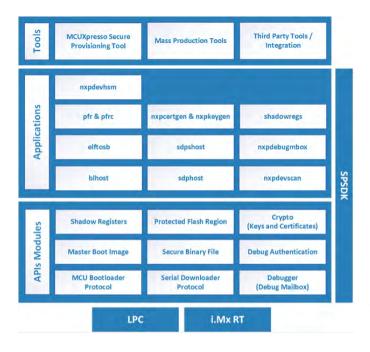

"blhost" is one component in a larger suite of tools found in the NXP Secure Provisioning SDK.

FIGURE 31. BLHOST IN THE CONTEXT OF THE NXP SECURE PROVISIONING SDK.

The NXP Secure Provisioning SDK is open source and can be found at <u>https://github.com/NXPmicro/spsdk</u>.

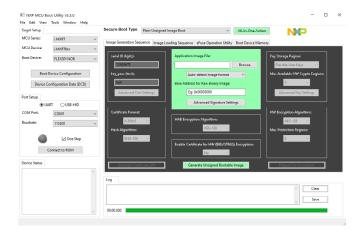

In addition to blhost, the MCUXpresso Secure Provisioning Tool can also be used to program images over the ISP interface. The MCUXpresso Secure Provisioning Tool provides an easy-to-use GUI for preparing bootable encrypted images and burning OTP fuses over the ISP interface. The GUI is built upon the tools in the NXP Secure Provisioning SDK. I find quite a bit of utility in the GUI tools as having a visual interface to the flash memory and OTP fuses can reduce mistakes. While you can always reprogram flash memory, a mistaken setting in the OTP fuses can be frustrating.

| tatus: 0 error(s), 3 warning(s). |         |        |       |         |   |                     |

|----------------------------------|---------|--------|-------|---------|---|---------------------|

| RETH 255 334                     | 0-0150  |        | ÷.    | 0       | ۷ |                     |

| OTP_MASTER_KEV[255               |         |        | _     | unknown |   |                     |

| OTP_MASTER_KEV[223               |         |        |       | unknown |   |                     |

| OTP_MASTER_KEV[191:              |         |        |       | unknown |   |                     |

| OTP_MASTER_KEV[159               |         |        | -     | unknown |   |                     |

| OTP MASTER KEV[127               |         |        |       | unknown |   |                     |

| OTP_MASTER_KEV[95:64]            |         |        | -     | unknown |   |                     |

| OTP_MASTER_KEV[63:32]            |         |        | _     | unknown |   | contents.           |

| OTP_MASTER_KEV[31:0]             | 0x01C0  |        | -     | unknown |   | Boot config         |

| OTFAD KEK SEED 127.96            |         |        | ă.    | 0       |   | Fuse descrip        |

| OTFAD KEK SEED 95 64             | 0x0188  |        | ď     | 0       |   | BOOT_PA             |

|                                  | 0x0184  |        | ă.    | 0       |   | BOOT_FA             |

| OTFAD_KEK_SEED_31_0              | 0x0180  |        | di la | 0       |   | DICE_SKI            |

| KEY_SCRAMBLE_SEED                | 0x01AC  | 107 10 | ef.   | 0       |   | SECURE_<br>DICE_INC |

| KEY STORE                        | ORC DAD | 100    | •     | v       |   | REDUNDA             |

| OTFAD_CFG                        | 0v01A8  | 106    | œ     | 0       |   | PSA_BSTA            |

| USB_ID                           |         | 105    | ۲     | 0       |   | PSA_BSTA            |

| USB_CFG                          |         | 404    | œ     |         |   | TZM_IMAG            |

FIGURE 32. MCUXPRESSO SECURE PROVISIONING TOOL - OTP FUSE GUI

The 2nd tool can be found in the <u>open-source</u> <u>community</u>.

An alternative to the NXP supported tools for ISP operations is the <u>"MCUBootUtility"</u> which can be found in the open-source community.

MCUBootUtility is a python-based GUI that wraps blhost to perform all of the most common operations. It supports the i.MX RT685 parts as well as all the other parts in the i.MX RT crossover family.

MCUBootUtility and the NXP Secure Provisioning SDK (which contains blhost) are both available as open source. One of the primary differences between the tools is that the Secure Provisioning SDK is officially supported by NXP. MCUBootUtility is supported by its author on GitHub.

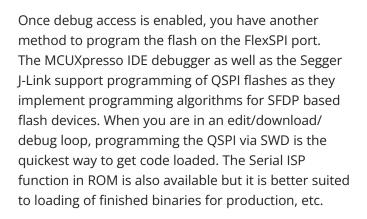

## i.MX RT685 Debug

The last piece we need to look at is debug access. The i.MX RT685 implements a standard ARM SWD interface. On my 1st design iteration with a new MCU, I always add the standard .050" ARM header for debug. The only connections needed for a minimal configuration are SWDCLK and SWDIO. Keep in mind that SWD trace IO are also available on the i.MX RT685, but I am choosing to use the simplest configuration. The only extra feature I added was Serial Wire Output (SWO). Once in a while, I will turn it on for streaming additional data through the debugger. However, I found that simple SWD is often good enough. I prefer to use Segger's J-Link and their Ozone debugger "but the MCUXpresso IDE can use low-cost debugger" should probably be "but the MCUXpresso IDE can be used with a low cost-debugger such as the MCU-Link. There is quite a bit you can get done with simple 2-wire SWD and the available tools.

FIGURE 34. i.MX RT685 DEBUG CONNECTIONS

In additional to the standard 0.050" debug header, I always add <u>Tag-Connect</u> pads for debug access. As the design progressed closer to the production build, the standard header can be added to the do not place list and the if debug as needed.

FIGURE 35. TAG-CONNECT SWD CABLE

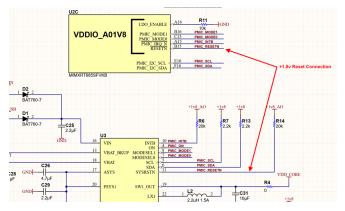

It should also be noted that the reset signal from the debug header may need a level translator. The reset connection from the PMIC to the i.MX RT685 is in the always on +1.8v power domain. IO Bank 1 in the Super-Monkey will be tied to a +3.3v rail. A simple solution is to use a simple open-drain buffer to connect the reset line into the PMIC/i.MX RT685 reset.

FIGURE 36. PMIC RESET CONNECTION.

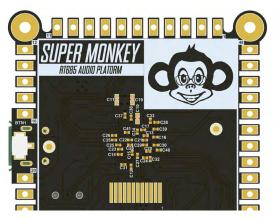

## Realizing the Super Monkey Hardware

There is quite a bit of IO available on the i.MX RT685, but I chose to constrain my design to the most common functions for real-time audio. My applications generally use professional, "flagship quality" audio codecs for musical instrument signal processing. Using this as a guide, the process of coming up with a minimal IO complement was simplified.

FIGURE 37. THE i.MX RT685 SUPER-MONKEY

I spent quite a bit of time considering a form factor. Since this was my first attempt at an i.MX RT685 design, I elected to constrain the formfactor to something known. Last year I developed the Mini-Monkey around the NXP LPC55S69. For the "Super-Monkey", I chose to keep this form factor but extend the number of IO. Decision making fatigue is a very real concern for engineers. The "perfect module form factor" trap is easy to fall into. It is tempting to spend a great deal of time optimizing for a general-purpose use case to handle unknown requirements. My experience has shown me that in almost every case, overthinking future possibilities at the outset never pays dividends down the road. We engineer's love to tinker and will end up making changes anyway. I have two separate projects I want to implement with the i.MX RT685, so I decided to focus my efforts exclusively on what I need.

I thought it would be instructive to list in Figure 35 some of the high-level processing capabilities available in the i.MX RT685. It is difficult to overstate the amount of capability packed into the i.MX RT685. Every few years I like to step back and reflect on progress that has been made with MCU integration. It is often too easy to overlook the sum of science & engineering needed to integrate this amount of technology in a 9mmx9mm package. All of it for a couple lattes at the coffee shop.

# Super-Monkey IO

#### **Power Input**

+5v from the micro-USB or IO connector. There is also JST "PH" connector for <u>common LiPO batteries</u>. PCA9420 PMIC has a built-in battery charger so the Super-Monkey can be "portable".

#### **Digital Audio IO**

The Super-Monkey has two I2S/TDM audio interfaces provided by the flexcomm peripheral. In my applications, I tend to separate the ADC and DAC to achieve the highest SNR. One channel will be used to interface with an 8-channel audio ADC (Cirrus Logic CS5368) and the other will be used with an AES3 Audio Transmitter (Cirrus Logic CS8406). The second channel will drive a professional audio DAC (Cirrus Logic CS4398). For some applications, I prefer the audio master clock to be generated with a highquality, minimal phase noise oscillator. The Super-Monkey has a pin that can be used to bring in an external master clock.

#### **Digital Microphones**

The Super-Monkey exposes all eight DMIC inputs available on the i.MX RT685.

#### **Spare Flexcomm**

I reserved pins for one Flexcomm port to be allocated on a per project basis. This will allow me to select I2C, SPI, UART or an extra I2S bus as needed.

#### **Debug UART**

There is one dedicated UART exposed via the IO pins. This UART can be used with the ROM bootloader to program flash, fuses, etc.

#### **I3C**

I reserved two pins to experiment with the I3C bus. I3C is a new superset of the I2C standard which allows for much faster data rates, multi-master and hot join capability. It lives at an interesting intersection of I2C and SPI, so I wanted a platform to run experiments.

#### SDIO

A 4-bit SDIO port for adding an SD card. I do not have an immediate requirement for SDIO but at a minimum I get a handful of GPIO that are also multiplexed with SCT (State Configuration Timer) channels. I \*really\* like the SCT in all the LPC families so I made sure to make it available.

#### ADC

I exposed three inputs to the i.MX RT685 1MSPS ADC, two of which can be used to form a fully differential input. The intent is to use the ADC channels for potentiometers/user input. I have plans for piezo vibration sensor applications as well.

#### LCD

I borrowed the 1.54" from the <u>LPC55S69 Mini-</u> <u>Monkey Design.</u> In fact, the module form factor was original designed around <u>this specific display.</u> It looks really sharp, so I decided to include it for some neat audio visualizations. The LCD is wired to a dedicated 50MHz high speed SPI port and can achieve high frame rates. Coupled with the large RAM in the i.MX RT685, the Super-Monkey can perform some interesting graphics applications.

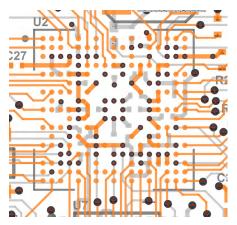

# Super Monkey PCB Routing

I intended the Super-Monkey to use a 4-layer PCB stackup. To achieve a 4-layer design, I had to make some compromises as compared to the layout on RT685-EVK. The RT686 in the VFBGA176 package is straightforward to fan out. In fact, the PCB routing on the RT685-EVK has all IO fanned out on the top layer. One caveat is that 3mil trace/space design rules are required The EVK is quite large and there is plenty of room to bring all the traces on the top layer. The Super-Monkey has more parts placed very close to the MCU package, so I needed to make use of the bottom layer near the package. As an alternative example to the RT685-EVK, I chose to use 5mil design rules coupled with via-in-pad technology to fan out the IO.

FIGURE 38. SUPER-MONKEY IO FANOUT

The via-in-pad geometry uses a 12-mil pad with 6mil mechanical drill. This geometry is on the edge of where laser microvias would be required. The two inner layers (not shown) are dedicated to return and power (Core, +1.8v and +3.3v). Via-in-pad allowed me to use a more relaxed 5mil trace/space rule which is a lower cost and higher yield option as compared to 3-mil. Since I did not require all the i.MX RT685 IO, keeping to a 4-layer design was straightforward. Via-in-pad does increase cost, but the trade-off vs 3-mil spacing makes it an attractive option to relax the clearance specifications and fanout to other layers. It also allows one place vias on the decoupling pad simplifying placement.

The VFBGA176 package does leave some balls unpopulated making routing and fanout simpler. Most of the core power and ground connectors are on the interior of the package. This alleviates quite a bit of contention with IO. In Figure 36, you can see the 0201 capacitors on the bottom side. I believe with some work, 0402 size capacitors could be used to relax manufacturing tolerances. 0201 capacitors are quite small. Chris Denny of Worthington assembly posted some nice blogs on optimum geometries <u>for</u> <u>high yield when using 0201</u> packages. He also has a nice article on <u>via-in-pad</u> technology.

It is certainly possible to route the i.MX RT685 VFBGA176 on a 4-layer process and still be able to use quite a bit of the IO. In fact, with a bit more work, I feel I could use about 90% of the IO before resorting to a 6-layer process. While this package is small, it is still possible to use it successfully without breaking the bank with high-cost PCB fabrication processes.

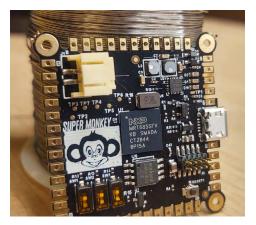

# SuperMonkey Board Build

For board fabrication and assembly, I used <u>CircuitHub</u>. CircuitHub handles all aspects of the fabrication process. All you need to do is upload your design files and CircuitHub will acquire the raw PCBs, procure the components, and stuff the boards. The CircuitHub workflow also allows for consigned parts. Given the current situation with the supply chain, this was a welcome feature. I was able to send them some of the parts that were not available through normal channels as I had "banked" a few of the components several months ago.

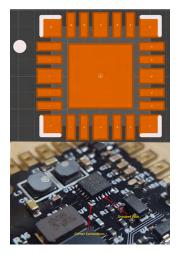

FIGURE 39. THE i.MX RT685 SUPERMONKEY

You can find <u>source files for the hardware design</u> on GitHub. caps in place of 0201 sized 0.1uF decoupling caps.

The specs for this board use a small drill requirement (6mil) and a tight annual ring (3mil). This drill geometry was used for filled via-in pad technology on the VFBGA176. I chose this approach for fanning out the VFBGA176 package as it enabled looser specs on trace space/width. The RT685-EVK did not use viain-pad technology, rather a 3mil trace space/width for escaping some of the signals. I elected to use a filled via-in-pad approach after some discussion with CircuitHub. The result was a fairly simple routing exercise on 4-layers. I do also want to point out that this design utilized 0201 sized decoupling capacitors. The 0201 decoupling capacitors were placed on the bottom side of the board directly under the i.MX RT685 MCU.

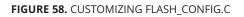

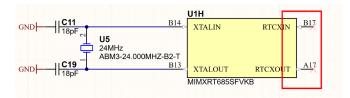

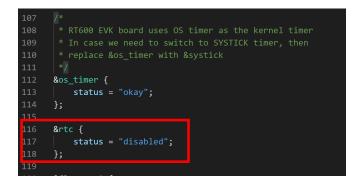

FIGURE 40. 0201 DECOUPLING CAPACITORS